DDR3 layout vs Memory chip fitting

Have you been thinking about leaving some of the memory chips un-fitted on your board and you were not sure if it’s possible or how the layout should be done to support it? I have received this question for couple of times, so I try to share what we tested and what we do.

We have two boards supporting partial memory fit, one uses T-Branch and one uses Fly-by topology. The boards were extensively tested and they work oki. However, in your application you may want to consider more factors, including maximum memory frequency. We tested the layout with memory clock 553MHz (when all memory chips were fitted) and 400MHz (when only part of the memory chips were fitted). We couldn’t test higher frequencies as this is the maximum what our CPU supports.

We tested the boards in environmental chamber running between -40°C to 65°C / -40°F to 149°F and tested them running memory tests for weeks, no problems.

We have two boards supporting partial memory fit, one uses T-Branch and one uses Fly-by topology. The boards were extensively tested and they work oki. However, in your application you may want to consider more factors, including maximum memory frequency. We tested the layout with memory clock 553MHz (when all memory chips were fitted) and 400MHz (when only part of the memory chips were fitted). We couldn’t test higher frequencies as this is the maximum what our CPU supports.

We tested the boards in environmental chamber running between -40°C to 65°C / -40°F to 149°F and tested them running memory tests for weeks, no problems.

Fly-by

We used this on our OpenRex project. You can download the complete Altium project and check by yourself how we did the schematic and layout. Download OpenRex files hereWhat memory chips are fitted?

We only fit the chips placed on the bottom data bus (D31-D0). The full data bus width is 64bits (four x16 memory chips), but in our 32bit configuration we only fit two x16 memory chips placed on memory data bus D31-D0.

DDR3 Schematic: Shows the chips connected to the bottom data bus (D31-D0)

Placement

We placed all the memory chips on one layer only (TOP side of PCB) and the two memory chips which are fitted (D31-D0) are at the end of the Fly-By (closest chips to the termination resistors, you can see the termination resistor at the end of the track).

Fly-by ADDR/CMD/CTL

We placed all the memory chips on one layer only (TOP side of PCB) and the two memory chips which are fitted (D31-D0) are at the end of the Fly-By (closest chips to the termination resistors, you can see the termination resistor at the end of the track).

Fly-by ADDR/CMD/CTL

Layout

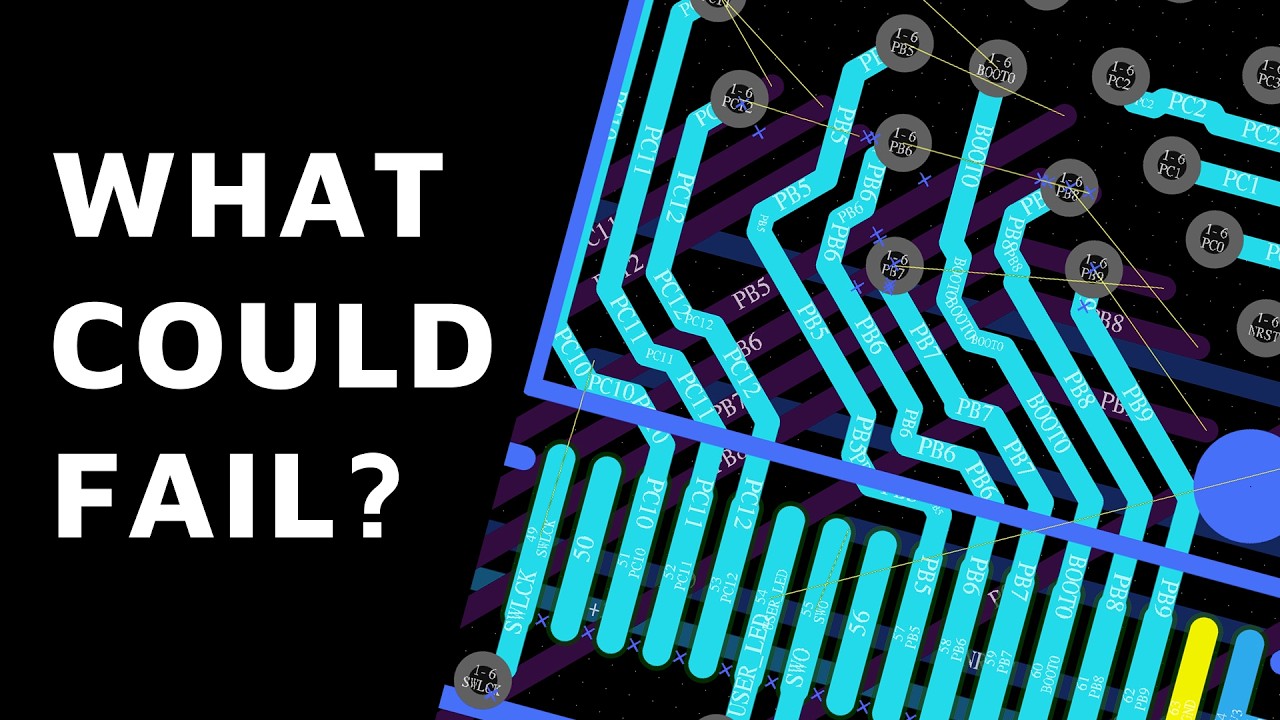

We tried to make the stubs on Address / Command / Control signals as short as possible. (Notice, the VIAs are placed close the the memory pads.)

ADDR/CMD/CTL stubs (Top layer)

We tried to make the stubs on Address / Command / Control signals as short as possible. (Notice, the VIAs are placed close the the memory pads.)

ADDR/CMD/CTL stubs (Top layer)

ADDR/CMD/CTL stubs (All layers)

T-Branch

We tested it on our TinyRex moduleWhat memory chips are fitted?

Again, we only fit the chips placed on the bottom data bus (D31-D0). The full data bus width is 64bits (four x16 memory chips), but in our 32bit configuration we only fit two x16 memory chips placed on memory data bus D31-D0.

Placement

We placed the D31-D0 memory chips on the TOP and D32-D63 on the bottom side of PCB. When running on half of the memory, the TOP memory chips are fitted and the bottom memory chips are not fitted.

Layout

If only the two memory chips on the TOP are fitted, there will be short stubs on the bottom, but we tested it and the boards are working oki.

ADDR/CMD/CTL layout

Data D31-D0 (TOP layer)

Data D31-D0 (All layers)